为世界上第一条 200mm 碳化硅中试线铺平道路

为世界上第一条 200mm 碳化硅中试线铺平道路

来源:

摘要

近年来,基于碳化硅(SiC)的电力电子行业迅速扩张,但供应商正在努力满足市场对最终设备和起始原材料的需求,如今这些原材料由直径为 150 毫米(6 英寸)的 SiC 晶片组成。为此,碳化硅电力电子领域的顶级工业企业开始着手开发直径为 200 毫米(8 英寸)的下一代晶圆。这项工作描述了最近在实施世界上第一条生产基于 200 毫米 SiC 晶片的功率器件的工业中试线方面取得的成果。特别是 200 mm SiC 晶锭的晶体生长、晶片的切片和抛光、外延层的沉积,并介绍了试点线路中的第一个测试。

1 . 引言

在过去的十年中,碳化硅(SiC) 已经从具有高潜力但存在可靠性问题的宽带隙半导体发展成为电力电子领域中不可或缺的首选材料 [ 1 , 2 ]。过去几年主要受电动汽车普及带动的 SiC 功率器件市场的扩张速度如此之快,以至于许多供应商都在努力满足对 SiC 功率器件的需求 [ 3 , 4 ],到目前为止,直径为 150 毫米(6 英寸)的晶圆。作为下一步打算,几家公司不仅通过投资 150 毫米晶圆厂来扩大其生产能力,而且还开始开发直径为 200 毫米(8 英寸)的下一代 SiC 晶圆 [ 5 ]。事实上,晶圆直径增加 50 毫米对应于 78% 的面积增大,因此,相同数量的每个晶圆的器件数量可能会增加。200 毫米 SiC 晶片的首次演示报告于 2015 年 [ 6 , 7 ],但晶体质量仍然比 150 毫米对应物差很多。在生产线上实际应用 200 mm SiC 晶片的时机尚未成熟。

2018年,一个名为REACTION(欧洲碳化硅八英寸试验线)的欧洲项目获得资助,旨在开发世界上第一条用于生产功率器件的200毫米碳化硅试验线设施[ [8]、[9]、[10]]。来自工业界和学术界的 27 个合作伙伴加入了该项目。不同合作伙伴一致认为,200mm SiC晶圆的发展必须达到两大里程碑,主要与材料的晶体质量有关:机械化学抛光晶圆和高质量晶圆。机械级晶圆的目的是支持与 200 毫米晶圆尺寸兼容的新生长反应器的开发,优化切片和抛光步骤,并测试中试生产线中不同生产工具的处理能力。出于这个原因,从晶体质量的角度来看,这些样品并不意味着可以与最先进的 150 毫米晶片相媲美。另一方面,在这项工作中,我们概述了该联盟为生产机械和开发级别的 200 毫米 SiC 晶片以及建立试生产线而执行的早期开发步骤。特别介绍了 200 mm SiC 晶锭的晶体生长、晶片的切片和抛光、外延层的沉积以及中试生产线的首次测试。

2 . 200 mm 4H-SiC 晶锭的晶体生长

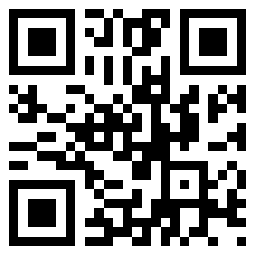

本工作中介绍的机械和开发级 200 mm 4H-SiC 晶片由 II-VI Incorporated 制造。所述的SiC晶锭使用与专有的反应器设计[物理气相传输(PVT)法生长11 ]。图 1显示了与本工作中使用的系统相似但不完全相同的通用 PVT 系统的示意图。反应器的核心是石墨坩埚,里面装有高纯度的碳化硅粉末和晶种。坩埚被感应加热到 2000 °C 以上的温度。在如此高的温度下,SiC 粉末升华,产生的蒸汽通过热梯度传输在坩埚内朝着单晶 SiC 晶种生长。晶种晶片作为进入蒸汽的成核中心,也用于

图1。用于SiC晶锭晶体生长的典型 PVD 反应器的示意图。

大量的生长实验运行,致力于支持 REACTION 项目的 200 毫米沉底的开发。由于晶种的直径和质量对晶片质量至关重要,因此大部分生长实验都集中在将高质量晶种扩展到大于 200 毫米的直径。

3 . 使用 SiC 晶锭制造 200 mm 外延晶圆

一旦SiC晶锭生长出来,就必须从它上切下晶片。制造过程的这一部分绝不是微不足道的,并且在产品的最终质量中起着至关重要的作用。事实上,晶圆切片的几个方面至关重要,例如晶体取向、产量最大化、材料损失和加工成本最小化、实现低缺陷表面等 。涉及不同的工艺工具,其中一些必须重新设计才能与 200 毫米晶圆一起使用。所有涉及的工具都需要对工艺参数进行微调,以确保从 150 毫米尺寸变为 200 毫米尺寸时具有良好的最终质量和产量。将生长的晶锭磨成 200 毫米直径,并通过多线锯成功切片。对所得原始晶片进行机械抛光和化学机械抛光,以获得标称厚度为 500 μm 的低粗糙度、外延就绪晶片。

已向项目合作伙伴交付了 50 多个直径为 200 毫米的单晶衬底。从形态学和电学角度对衬底进行表征。通过 FlatMaster 200 测量的交付晶圆的平均厚度为 500.8 μm,这表明切片工艺提供了良好的晶圆到晶圆再现性。发现平均总晶片内厚度变化 (TTV) 约为 5.9 μm。交付晶圆的平均翘曲为 46 μm;虽然这个值还有待改善,但它应该已经能够使用中试线的制造工具。通过非接触式映射系统 LEI 1510 测量的晶片电阻率在交付的样品中具有 22.8 mΩ∙cm 的平均值,晶片内的变化小于 3%。该电阻率值正好在 15-25 mΩ∙cm 的目标范围内。

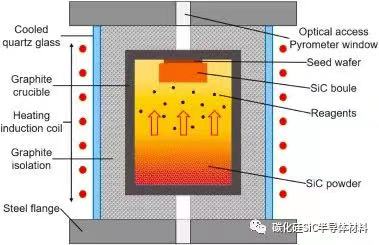

为了量化基板中的晶体缺陷分布,使用熔融 KOH 浴进行选择性蚀刻[ 13 ]。所采用的 KOH 溶液在螺纹刃位错(TED) 和螺纹螺型位错(TSD)方面比常规 KOH 浴更具选择性。事实上,TSD 的蚀刻速率高于 TED,导致 TSD 的蚀刻坑比 TED 更大,这可以根据显微镜图像轻松区分。螺纹混合位错 (TMD) 将被视为 TSD,而基面位错密度(BPD) 很容易被识别。通过自动 Sica 系统对选择性蚀刻产生的表面特征进行分析。

图 2显示了总缺陷密度(DD)、BPD 和 TSD 晶片图,通过对来自两个不同生长运行的晶片进行选择性蚀刻获得。特别是,图 2 (a)–(c) 中的图是指在 200 mm 晶圆开发的早期阶段生产的晶圆(以下称为样品 A),而图 2 (d)–(f)中的图) 是在使用改进的生长工艺生长的晶片上获得的(以下称为样品 B)。样品 A 的总 DD 的平均值大约为 11,000 cm -2,晶片内的 BPD 变化很大,如图2 (b) 所示。样品 A 的平均位错密度为 11,256 cm -2、1807 cm -2和 3739 cm-2 分别表示 DD、BPD 和 TSD。相比之下,样品 B 的总 DD 小于 4000 cm -2,即几乎比样品 A 低三倍。样品 B 的平均位错密度为 3885 cm -2、951 cm -2和 716 cm - 2为DD,BPD和TSD,分别。与样品A相比,这是一个显着的改进;样品 B 的 DD 改进归因于更好的晶种晶体质量和优化的生长参数。这对于未来高质量 200 mm SiC 晶片的发展来说是一个很有希望的结果。值得注意的是在 0.25 cm -2的晶片上测得的平均微管密度低于 0.5 cm -2的目标并且已经非常接近商用 150 mm SiC n 型衬底的当前值,即<1 cm -2。

图2。从样品 A (a)–(c) 和样品 B (d)–(f) 的选择性湿蚀刻测试中获得的DD 、BPD和TSD 的晶圆图。

4 . 生产工具的初步处理和兼容性测试

II-VI Incorporated 生产的部分机械级晶圆被送往意法半导体 (STM),使用 200 毫米SiC 中试线的工业生产工具进行处理和兼容性测试。事实上,晶圆的厚度和电阻率波动、弯曲、边缘碎裂和表面缺陷等特征会严重影响甚至损坏生产线上的一些工具。因此,必须进行初步的兼容性测试。

值得注意的是,STM 能够在功率器件生产所需的主要工具内处理 200 毫米 SiC 晶片,例如自动检测工具、光刻步进机、注入机、用于热处理和氧化物生长的烤箱、用于沉积电介质和金属薄膜、湿法蚀刻台、洗涤器等。这些测试的成功确实是实现工业试验线的基本步骤,这需要 STM 方面的大量经济和技术投资。

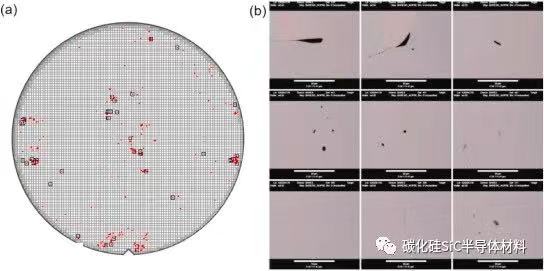

第一批晶圆在边缘处显示出很少的小芯片,这导致了工具内的对齐问题。II-VI Incorporated 解决并迅速解决了边缘芯片的形成问题。图 3显示了在 STM 生产线上对 200 毫米 SiC 晶片进行的缺陷图和自动电子显微镜检查的示例。在基材表面发现了一些缺陷,主要是划痕和凹坑。缺陷的类型和位置表明晶片制造过程中的切片和抛光步骤需要进一步优化。

图3。(A) 使用 Altair 系统获得的 200 毫米机械级晶圆的典型缺陷图和 (b)在 STM 试验线中执行的相应自动电子显微镜检查。左上角的前五幅图像是与晶体缺陷相关的凹坑,而其他四幅图像则显示了可能由切片和抛光步骤引起的划痕。

5 . 在 200 mm SiC 晶片上生长 4H-SiC 外延层

为了进一步改善晶体质量和用于前端工艺制备晶片,在晶片的化学-机械抛光的侧通常被沉积的外延层的碳化硅。在 REACTION 项目的框架内,LPE Spa 负责开发一种新的化学气相 (CVD) 反应器,用于在 200 毫米晶圆上生长 SiC 外延层。

在 200 毫米晶圆上开发 SiC 外延层由 LPE Spa 在其位于卡塔尼亚的实验室开始,使用原型 CVD 反应器不控制晶圆旋转并配备单区气体注入系统。第一个原型将在 REACTION 项目期间得到改进,上述功能将包含在反应器的最终版本中。

n 型 4H-SiC 外延层的生长是在 1600 °C 以上的温度下进行的,使用三氯硅烷 (SiHCl 3 ) 和乙烯 (C 2 H 4 ) 作为前驱体 [ 14 ],氮作为 n 型掺杂气体。以这种方式实现了高达 30 μm/h 的生长速度。产生标称厚度为6.5μm且施主掺杂浓度为9.5×10 15 cm -3的外延层。生长后,沉积的外延层的厚度通过红外快速傅里叶变换光谱 (FTIR) 测量,而掺杂浓度则通过汞探针获得的电容测量值估算。

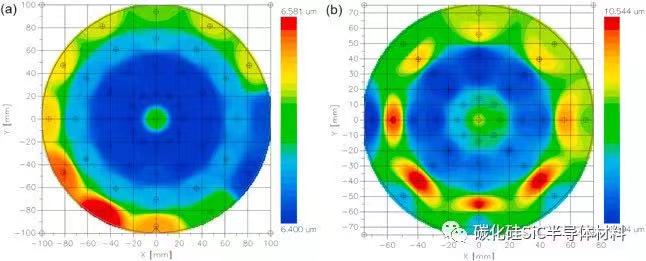

图 4 (a) 显示了通过原型 CVD 反应器沉积在 200 毫米机械级 SiC 晶片上的外延层的典型厚度图。晶圆厚度的平均值为 6.44 μm,标准偏差为 0.05 μm。晶片厚度均匀性,评估为标准偏差与平均值之间的比率,为 0.8%。观察到外延层厚度从中心到边缘略微径向增加,小于 0.2 μm;厚度图的不对称性主要是由于原型反应器中的单区气体注入。图 4 (b) 显示了由 LPE Spa 在商用 150 mm SiC 晶片上通过标准 CVD 反应器沉积的外延层厚度图 [ 15]]。晶圆厚度的平均值为 10.45 μm,标准偏差为 0.04 μm。在这种情况下,晶片厚度均匀度为 0.4%,因此,非常接近使用原型反应器在 200 毫米晶片上获得的值。

图 4。(a) 200 mm 机械级SiC晶片和 (b) 商用 150 mm SiC 晶片上外延层的典型厚度图。

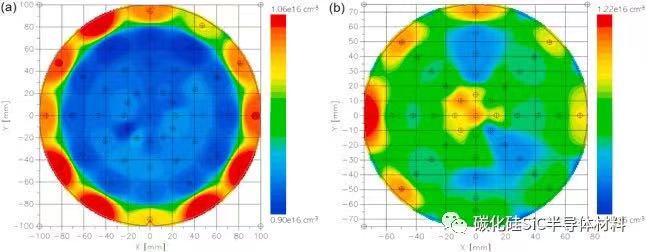

图5(a)和(b)显示了对应于图4中已经呈现的外延层的掺杂图,分别生长在(a)200mm SiC晶片和(b)150mm SiC商业晶片上。200mm晶圆的平均掺杂值为9.54×10 15 cm -3,标准偏差为0.53×10 15 cm -3,晶圆掺杂均匀度为5.6%。

另一方面,商用 150 mm 晶圆的平均掺杂值为 11.9 × 10 15 cm -3,标准偏差为 0.14 × 10 15 cm -3,以及 1.1% 的晶圆掺杂均匀度。尽管机械级 200 毫米晶圆已经显示出良好的厚度和掺杂分布,但使用更先进的 200 毫米外延反应器最终版本,掺杂的晶圆均匀性将得到改善。

图 5。(a) 200 mm 机械级SiC晶片和 (b) 商用 150 mm SiC 晶片上外延层的典型掺杂图。

6 . 总结

这项工作概述了最近在 REACTION 项目框架内获得的基于 200 毫米SiC晶片的世界上第一条工业试验线的实施取得的成就。回顾了用于 200 毫米 SiC 晶锭晶体生长的新型 PVD 反应器的开发,并描述了将晶锭切成外延就绪晶片的步骤。通过使用熔融 KOH 进行选择性蚀刻来评估由早期生长运行产生的晶片的晶体质量。测量证明,衬底的晶体质量超过了项目最初为初步开发阶段设定的要求,并且在微管密度方面甚至非常接近商用 150 mm SiC n 型衬底的当前值.

此外,还描述了使用原型 CVD 系统在 200 毫米晶圆上沉积 SiC 外延层,并介绍了沉积在机械级晶圆上的薄膜的主要特征。测量结果表明,外延层厚度在 200 毫米晶圆的整个表面上非常均匀,与在 150 毫米商用晶圆上获得的均匀性相似。掺杂均匀性也相当不错,但仍与通常在 150 毫米对应物中获得的一致。此外,试生产线的许多生产工具都使用机械级晶圆进行了测试,并成功证明了它们与 200 mm SiC 的兼容性。总之,这项工作朝着在 200 mm SiC 晶片上制造下一代功率器件迈出了重要的一步。

(声明:本文版权归原作者所有,转发仅为更大范围传播,若有异议请联系我们修改或删除:wang@cgbtek.com)